- 您现在的位置:买卖IC网 > Sheet目录2011 > MAX5856AECM+D (Maxim Integrated Products)IC DAC 8BIT DUAL 300MSPS 48-TQFP

General Description

The MAX5856A dual, 8-bit, 300Msps digital-to-analog

converter (DAC) provides superior dynamic performance

in wideband communication systems. The MAX5856A

integrates two 8-bit DAC cores, 4x/2x/1x programmable

digital interpolation filters, phase-lock loop (PLL) clock

multiplier, and a 1.24V reference. The MAX5856A sup-

ports single-ended and differential modes of operation.

The MAX5856A dynamic performance is maintained over

the entire power-supply operating range of 2.7V to 3.3V.

The analog outputs support a compliance voltage of

-1.0V to +1.25V.

The 4x/2x/1x programmable interpolation filters feature

excellent passband distortion and noise performance.

Interpolating filters minimize the design complexity of ana-

log reconstruction filters while lowering the data bus and

the clock speeds of the digital interface. The PLL multiplier

generates all internal synchronized high-speed clock sig-

nals for interpolating filter operation and DAC core conver-

sion. The internal PLL helps minimize system complexity

and lower cost. To reduce the I/O pin count, the DAC can

also operate in interleave data mode. This allows the

MAX5856A to be updated on a single 8-bit bus.

The MAX5856A features digital control of channel gain

matching to within ±0.4dB in sixteen 0.05dB steps.

Channel matching improves sideband suppression in

analog quadrature modulation applications. The on-chip

1.24V bandgap reference includes a control amplifier

that allows external full-scale adjustments of both chan-

nels through a single resistor. The internal reference can

be disabled and an external reference may be applied

for high-accuracy applications.

The MAX5856A features full-scale current outputs of

2mA to 20mA and operates from a 2.7V to 3.3V single

supply. The DAC supports three modes of power-control

operation: normal, low-power standby, and complete

power-down. In power-down mode, the operating cur-

rent is reduced to 1A.

The MAX5856A is packaged in a 48-pin TQFP with

exposed paddle (EP) for enhanced thermal dissipation

and is specified for the extended (-40°C to +85°C) opera-

ting temperature range.

Applications

Communications

SATCOM, LMDS, MMDS, HFC, DSL, WLAN,

Point-to-Point Microwave Links

Wireless Base Stations

Direct Digital Synthesis

Instrumentation/ATE

Features

8-Bit Resolution, Dual DAC

300Msps Update Rate

Integrated 4x/2x/1x Interpolating Filters

Internal PLL Multiplier

2.7V to 3.3V Single Supply

Full Output Swing and Dynamic Performance at

2.7V Supply

Superior Dynamic Performance: 68dBc SFDR at

fOUT = 20MHz

Programmable Channel Gain Matching

Integrated 1.24V Low-Noise Bandgap Reference

Single-Resistor Gain Control

Interleave Data Mode

Differential Clock Input Modes

EV Kit Available—MAX5858AEVKIT

MAX5856A

Dual 8-Bit, 300Msps DAC with 4x/2x/1x

Interpolation Filters and PLL

________________________________________________________________ Maxim Integrated Products

1

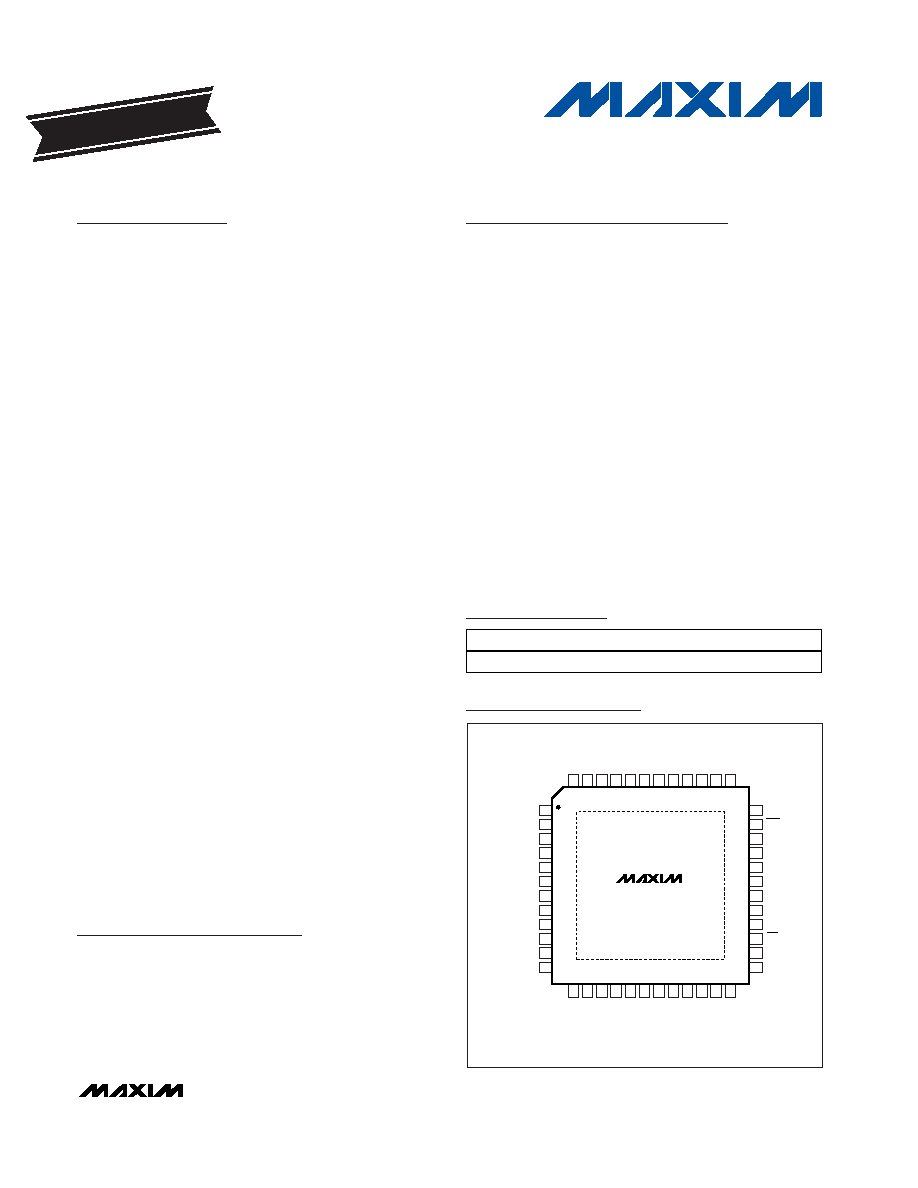

TQFP-EP

1

2

3

4

5

6

7

8

9

10

11

12

36

35

34

33

32

31

30

29

28

27

26

25

13 14 15 16 17 18 19 20 21 22 23 24

48 47 46 45 44 43

EP

42 41 40 39 38 37

DB7

DB6

DB5

DB4

DB3

DV

DD

DGND

CLK

IDE

DB2

DB1

DB0

DV

DD

DGND

AV

DD

OUTPA

OUTNA

AGND

OUTPB

OUTNB

AV

DD

REFR

N.C.

DA7/PD

DA6/DACEN

DA5/F2EN

DA4/F1EN

DA3/G3

DGND

DVDD

DA2/G2

DA1/G1

DA0/G0

N.C.

REF0

PLLF

PGND

PVDD

CLKXN

CLKXP

PLLEN

LOCK

N.C.

CW

REN

NOTE: EXPOSED PADDLE CONNECTED TO GND.

MAX5856A

TOP VIEW

Pin Configuration

Ordering Information

19-3019; Rev 1; 3/04

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

EVALUATION

KIT

AVAILABLE

PART

TEMP RANGE

PIN-PACKAGE

MAX5856AECM

-40°C to +85°C

48 TQFP-EP*

*EP = Exposed paddle.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX5858AECM+D

IC DAC 10BIT DUAL 300MSPS 48TQFP

MAX5858ECM+D

IC DAC 10BIT DUAL 300MSPS 48TQFP

MAX5863ETM+T

IC AFE 8/10BIT 7.5MSPS 48-TQFN

MAX5864ETM+T

IC ANLG FRONT END 22MSPS 48-TQFN

MAX5865ETM+T

IC ANLG FRONT END 40MSPS 48-TQFN

MAX5866ETM+

IC ANLG FRONT END 60MSPS 48-TQFN

MAX5873EGK+D

IC DAC 12BIT 200MSPS DUAL 68-QFN

MAX5874EGK+D

IC DAC 14BIT 200MSPS DUAL 68-QFN

相关代理商/技术参数

MAX5856AECM+TD

功能描述:数模转换器- DAC 8-Bit 2Ch 300Msps DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5856AECM-D

功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5856AECM-TD

功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5858AECM

制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述:

MAX5858AECM+D

功能描述:数模转换器- DAC 10-Bit 2Ch 300Msps DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5858AECM+TD

功能描述:数模转换器- DAC 10-Bit 2Ch 300Msps DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5858AECM-D

功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

MAX5858AECM-TD

功能描述:数模转换器- DAC RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube